# Impact of contact resistance on the electrical properties of MoS<sub>2</sub> transistors at practical operating temperatures

Filippo Giannazzo<sup>\*1</sup>, Gabriele Fisichella<sup>1</sup>, Aurora Piazza<sup>1,2,3</sup>, Salvatore Di Franco<sup>1</sup>, Giuseppe Greco<sup>1</sup>, Simonpietro Agnello<sup>2</sup> and Fabrizio Roccaforte<sup>1</sup>

## Full Research Paper

Address:

<sup>1</sup>Consiglio Nazionale delle Ricerche – Istituto per la Microelettronica e Microsistemi, Strada VIII, n 5, 95121 Catania, Italy, <sup>2</sup>Department of Physics and Chemistry, University of Palermo, Via Archirafi 36, 90143 Palermo, Italy and <sup>3</sup>Department of Physics and Astronomy, University of Catania, Via Santa Sofia, 64, 95123 Catania, Italy

Email:

Filippo Giannazzo\* - filippo.giannazzo@imm.cnr.it

\* Corresponding author

Keywords:

contact resistance; mobility;  $\mbox{MoS}_2;$  temperature dependence; threshold voltage

Beilstein J. Nanotechnol. 2017, 8, 254–263.

doi:10.3762/bjnano.8.28

Received: 14 September 2016 Accepted: 03 January 2017 Published: 25 January 2017

This article is part of the Thematic Series "Self-assembly of nanostructures and nanomaterials II".

Guest Editor: I. Berbezier

© 2017 Giannazzo et al.; licensee Beilstein-Institut. License and terms: see end of document.

#### Abstract

Molybdenum disulphide (MoS<sub>2</sub>) is currently regarded as a promising material for the next generation of electronic and optoelectronic devices. However, several issues need to be addressed to fully exploit its potential for field effect transistor (FET) applications. In this context, the contact resistance, R<sub>C</sub>, associated with the Schottky barrier between source/drain metals and MoS<sub>2</sub> currently represents one of the main limiting factors for suitable device performance. Furthermore, to gain a deeper understanding of MoS<sub>2</sub> FETs under practical operating conditions, it is necessary to investigate the temperature dependence of the main electrical parameters, such as the field effect mobility (μ) and the threshold voltage (V<sub>th</sub>). This paper reports a detailed electrical characterization of back-gated multilayer MoS<sub>2</sub> transistors with Ni source/drain contacts at temperatures from T = 298 to 373 K, i.e., the expected range for transistor operation in circuits/systems, considering heating effects due to inefficient power dissipation. From the analysis of the transfer characteristics  $(I_D - V_G)$  in the subthreshold regime, the Schottky barrier height ( $\Phi_B \approx 0.18 \text{ eV}$ ) associated with the Ni/MoS<sub>2</sub> contact was evaluated. The resulting contact resistance in the on-state (electron accumulation in the channel) was also determined and it was found to increase with T as  $R_{\rm C}$  proportional to  $T^{3.1}$ . The contribution of  $R_{\rm C}$  to the extraction of  $\mu$  and  $V_{\rm th}$ was evaluated, showing a more than 10% underestimation of  $\mu$  when the effect of  $R_{\rm C}$  is neglected, whereas the effect on  $V_{\rm th}$  is less significant. The temperature dependence of  $\mu$  and  $V_{th}$  was also investigated. A decrease of  $\mu$  proportional to  $1/T^{\alpha}$  with  $\alpha = 1.4 \pm 0.3$ was found, indicating scattering by optical phonons as the main limiting mechanism for mobility above room temperature. The value of  $V_{\rm th}$  showed a large negative shift (about 6 V) increasing the temperature from 298 to 373 K, which was explained in terms of electron trapping at MoS<sub>2</sub>/SiO<sub>2</sub> interface states.

Open Access

### Introduction

Transition metal dichalcogenides (TMDs) are compound materials formed by the Van der Waals stacking of MX2 layers (where M = Mo, W, etc., i.e., a transition metal, and X = S, Se, Te, i.e., a chalcogen atom). Among the large number of existing layered materials [1], TMDs are currently attracting increasing scientific interest due to some distinct properties, such as the presence of a sizable bandgap in their band structure. As an example, MoS2 (the most studied among TMDs due to its high abundance in nature and relatively high stability under ambient conditions) exhibits an indirect bandgap of ≈1.3 eV in the case of few layers and bulk material and a direct bandgap of ≈1.8 eV in the case of a single layer. These properties make MoS2 an interesting material for the next generation of electronics and optoelectronics devices [2]. As an example, field effect transistors with very interesting performance in terms of the on/off current ratio ( $10^6$ – $10^8$ ) and low subthreshold swing ( $\approx 70 \text{ meV/}$ decade) have been demonstrated using single [3] and multilayers of MoS<sub>2</sub> [4].

MoS<sub>2</sub> thin films, obtained either by cleavage from the bulk material or by chemical vapor deposition, are typically unintentionally n-type doped. Since well-assessed methods for doping enrichment of MoS<sub>2</sub> under source/drain contacts are still lacking, MoS<sub>2</sub> transistors are mostly fabricated by deposition of metals directly on the unintentionally doped material, resulting in the formation of Schottky contacts. Experimental investigations showed that both low work function (e.g., Sc, Ti) and high work function (e.g., Ni, Pt) metals mostly exhibit a Fermi level pinning close to the conduction band of MoS<sub>2</sub> [5], resulting in a Schottky barrier height (SBH) for electrons typically ranging from 0.1 to 0.3 eV. The origin of this Fermi level pinning is currently a matter of investigation and a crucial role seems to be played by nanoscale defects/inhomogeneities at the metal/MoS<sub>2</sub> interface [6,7].

The presence of this small but not negligible Schottky barrier at source/drain contacts certainly has a strong impact on the electrical characteristics of  $MoS_2$  transistors in the subthreshold regime [5]. In addition, the resulting source/drain contact resistance,  $R_C$ , can also have a significant influence on the electrical properties of the device in the on-state, i.e., above the threshold voltage ( $V_{th}$ ). In particular,  $R_C$  is expected to affect, to some extent, the values of  $V_{th}$  and of the field effect mobility  $\mu$  extracted from the transfer characteristics (drain current,  $I_D$ , vs gate bias,  $V_G$ ) of the device and of the on-resistance ( $R_{on}$ ) extracted from the output characteristics (drain current,  $I_D$ , vs drain bias,  $V_{DS}$ ). Clearly, all these parameters ( $V_{th}$ ,  $\mu$ , and  $R_{on}$ ) have their own dependence on the temperature, and their combination results in the device electrical characteristics at a fixed measurement condition. Hence, to gain a deeper understanding

of the behavior of  $MoS_2$  transistors for real applications, a temperature-dependent characterization of the main electrical parameters under practical operating conditions is mandatory. A temperature range from room temperature to 400 K is a realistic range for device operation in circuits/systems, taking into account the heating effect they undergo due to inefficient heat dissipation. However, to date, only a limited number of papers have focused on the high temperature behavior of  $MoS_2$  transistors [8,9].

In this paper, we report a detailed temperature dependent investigation of multilayer MoS2 transistors with Ni source/drain contacts, focusing on the role played by the contact both in the subthreshold regime and above the threshold voltage. In contrast to other literature works, mainly focused on the use of low work function contacts (such as Sc or Ti) to minimize the effect of contact resistance in n-type MoS<sub>2</sub> FETs [5], we focused on a high work function metal such as Ni in this paper in order to evaluate the impact of Ni/MoS2 contact resistance on the device field effect mobility  $\mu$  and threshold voltage  $V_{\text{th}}$ . The interest on Ni was also motivated by the recently demonstrated possibility to achieve MoS<sub>2</sub> FETs with ambipolar behavior by performing a temperature-bias annealing processes on as-deposited Ni contacts [10]. In the following, the temperature dependence of  $\mu$ ,  $V_{\text{th}}$  and  $R_{\text{C}}$  in the range from 298 to 373 K was determined and the physical mechanisms of these dependences were discussed.

## Results and Discussion

Back-gated transistors have been fabricated using multilayer  $MoS_2$  flakes (with thickness ranging from  $\approx$ 40 to  $\approx$ 50 nm) exfoliated from bulk molybdenite crystals onto a highly doped Si substrate covered with 380 nm thick, thermally grown  $SiO_2$ . Such relatively thick  $MoS_2$  samples have been chosen since it has been reported that the electrical properties ( $\mu$ ,  $V_{th}$ ) of simple back-gated transistors fabricated with multilayer  $MoS_2$  are much less affected by the effect of the external environment (water/oxygen) [9] with respect to single or few layer devices [11], for which encapsulation is instead required to achieve good electrical performance [3].

Furthermore, as reported in the literature, carrier mobility is only slightly dependent on  $MoS_2$  thickness for transistors fabricated on  $\approx 20$  to  $\approx 70$  nm thick flakes, whereas stronger variations are observed for thinner flakes, with the largest mobility values obtained for thicknesses ranging from 6 to 12 nm [5].

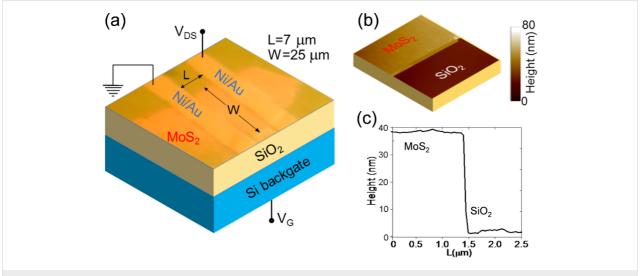

The experiments discussed in this paper have been carried out on a set of ten FETs fabricated on the same substrate. For consistency, the reported temperature-dependent analysis has been carried out on one of the transistors from this set of devices. Figure 1a shows a schematic representation including an optical image of a  $MoS_2$  transistor with the  $SiO_2/Si$  backgate and Ni/Au source and drain contacts. An atomic force microscopy image (Figure 1b) and the corresponding height linescan (Figure 1c) of the  $MoS_2$  flake on the  $SiO_2$  substrate are also reported, showing  $\approx 40$  nm flake thickness.

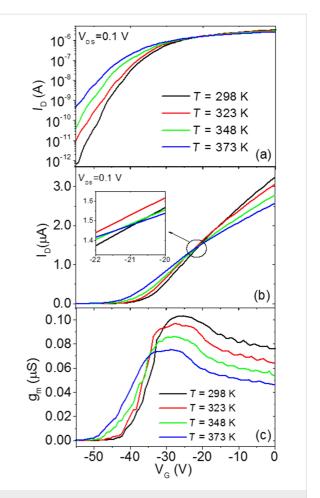

The transfer characteristics  $(I_{\rm D}-V_{\rm G})$  measured at a low fixed drain bias  $(V_{\rm DS}=0.1~{\rm V})$  on this device at different temperatures from 298 to 373 K are reported in Figure 2 both on a semilogarithmic scale (Figure 2a) and on a linear scale (Figure 2b). Clearly, the linear scale plot allows the current transport above the threshold voltage  $(V_{\rm th})$  to be studied, whereas the semilog scale plot allows for a better visualization of transport in the subthreshold regime. In the following two sections, a detailed analysis of the characteristics in the subthreshold and above-threshold regime will be reported and the device electrical parameters will be extracted. In particular, the Ni/MoS<sub>2</sub> Schottky barrier height and the flat band voltage  $(V_{\rm FB})$  will be evaluated from the temperature-dependent analysis of the subthreshold  $I_{\rm D}-V_{\rm G}$  curves, whereas the temperature behavior of  $V_{\rm th}$  and  $\mu$  will be obtained from the curves above the threshold.

#### Subthreshold behavior

The semilog scale  $I_D$ – $V_G$  characteristics (Figure 2a) measured at 298 K exhibit a current variation of more than six orders of magnitude in the bias range from  $V_G$  = -55 V to 0 V. This current variation is significantly reduced with increasing the temperature from 298 to 373 K, especially due to the strong increase of current with the temperature at large negative bias.

**Figure 2:** Semilog scale plot (a) and linear scale plot (b) of the transfer characteristics  $(I_D - V_G)$  measured at a fixed drain bias  $(V_{DS} = 0.1 \text{ V})$  and at different temperatures ranging from 298 to 373 K. (c) Transconductance  $(g_m = dI_D/dV_G)$  vs  $V_G$  curves at different temperatures calculated from the  $I_D - V_G$  characteristics in (b).

Figure 1: (a) Schematic including an optical image of a  $MoS_2$  transistor with the  $SiO_2/Si$  backgate and Ni/Au source and drain contacts. (b) Atomic force microscopy image and (c) the corresponding height linescan of the  $MoS_2$  flake on the  $SiO_2$  substrate.

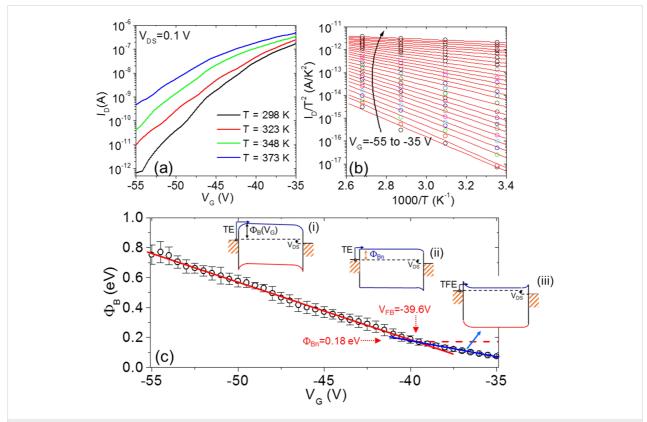

This is better highlighted in Figure 3a, where the  $I_D$ – $V_G$  characteristics in the gate bias range from -55 to -35 V and at different temperatures from 298 to 373 K have been reported. Such strong dependence of  $I_D$  on T suggests that current transport in the subthreshold regime is dominated by thermionic current injection through the reverse biased source/MoS2 Schottky contact, according to the relation  $I_D \propto T^2 \exp[-q\Phi_B(V_G)/k_BT]$ [5], where  $\Phi_{\rm B}(V_{\rm G})$  is the effective Schottky barrier height (SBH), modulated by the gate bias  $V_G$ . To verify this, for each  $V_{\rm G}$  an Arrhenius plot of  $I_{\rm D}/T^2$  vs 1000/T is reported in Figure 3b. A nice linear dependence was observed for all the  $V_G$ in the considered bias range. The effective SBH values  $\Phi_{\rm B}$ , obtained from the slope of the linear fit of the Arrhenius plot in Figure 3b are reported in Figure 3c as a function of  $V_G$ . The schematic band diagrams corresponding to the different transistor operation regimes, i.e., depletion (i), flat band (ii) and accumulation (iii), are also illustrated in the inserts of Figure 3c.

In the depletion regime (Figure 3c (i)), the applied gate bias induces an upward band bending,  $\psi$ , in MoS<sub>2</sub> at the interface with the SiO<sub>2</sub> gate insulator. The experimentally evaluated SBH is found to depend linearly on  $V_G$ . This dependence can be fitted with the relation  $\Phi_B = \Phi_B \left( V_{FB} \right) - \gamma \left( V_G - V_{FB} \right)$ , where

$Φ_B(V_{FB})$  is the effective SBH at the flat band voltage and the term  $ψ = γ(V_G - V_{FB})$  is the upward band bending. The slope γ indicates the modulation efficiency of  $Φ_B$  by the gate bias. It depends on the SiO<sub>2</sub> layer capacitance,  $C_{\rm ox} = ε_0 ε_{\rm ox} / t_{\rm ox} \approx 9.1 \times 10^{-5} \ {\rm F/m^2}$  ( $ε_0$  is the vacuum dielectric constant,  $ε_{\rm ox} = 3.9$ ,  $t_{\rm ox} = 380$  nm, the permittivity and the thickness of the SiO<sub>2</sub> film, respectively), on the capacitance of the MoS<sub>2</sub> depletion region,  $C_{\rm s}$ , as well as on the capacitance associated with MoS<sub>2</sub>/SiO<sub>2</sub> interface traps,  $C_{\rm it}$  [5]. In the depletion regime, the current transport in the transistor is ruled by thermionic emission (TE) of electrons from the source contact to the channel.

The effective SBH  $\Phi_B$  and, hence, the band bending  $\psi = \Phi_B(V_G) - \Phi_B(V_{FB})$  is found to decrease linearly moving toward positive  $V_G$  values. The flat band voltage  $V_{FB}$  corresponds to the gate bias for which  $\psi = 0$  (see (ii) in Figure 3b), whereas for  $V_G > V_{FB}$  the band bending  $\psi < 0$  (see (iii) in Figure 3b), i.e., the channel starts to accumulate electrons. In the accumulation regime, current injection in the channel is ruled by thermionic field emission (TFE) through the source triangular barrier. The TFE mechanism yields a reduced effective SBH with respect to the constant  $\Phi_B$  value (red dashed line in Figure 3c) that would be expected if only TE over the barrier would occur. As a guide

Figure 3: (a) Semilog scale plot of the transfer characteristics  $(I_D - V_G)$  in the subthreshold regime at different temperatures ranging from 298 to 373 K. (b) Arrhenius plot of  $I_D/T^2$  vs 1000/T for each gate bias. (c) Effective SBH  $\Phi_B$  as a function of  $V_G$ . In the inserts, schematic band diagrams are given for the transistor operation in different regimes: depletion (i), flat band voltage (ii) and accumulation (iii).

for the eye, the SBH dependence on  $V_{\rm G}$  in the accumulation regime has been fitted with a blue line in Figure 3c. Hence,  $V_{\rm FB} = -39.6$  V can be experimentally determined as the bias corresponding to the intercept between the two linear fits [5]. The corresponding SBH value  $\Phi_{\rm B}(V_{\rm FB}) = 0.18$  eV represents the "real" (i.e., gate bias independent) value of the Ni/MoS<sub>2</sub> Schottky barrier.

The experimental  $V_{\rm FB}$  for the MoS<sub>2</sub> transistor exhibits a large negative value, as reported in other literature works [12]. Such a result has been ascribed to donor-like interface trap states (positively charged when empty) between the SiO<sub>2</sub> and MoS<sub>2</sub> [13,14]. In order to evaluate the amount of this positive charge at the interface, it is worth comparing the experimental value with the one deduced from theoretical expression of the flat band voltage ( $V_{\rm FB,id}$ ) of an ideal metal-oxide-semiconductor field effect transistor (i.e., without fixed or interface charges).  $V_{\rm FB,id}$  is expressed as [15]:

$$V_{\mathrm{FB,id}} = W_{\mathrm{M}} - \left[ \chi + E_{\mathrm{G}} / 2 - kT / q \ln \left( N_{\mathrm{D}} / n_{\mathrm{i}} \right) \right], \tag{1}$$

where  $W_{\rm M}$  is the work function of the gate material (4.05 eV for the n<sup>+</sup>-doped Si back gate in our transistor),  $\chi$  is the semiconductor electron affinity (4.2 eV for MoS<sub>2</sub>),  $N_{\rm D}$  is the semiconductor doping concentration (on the order of  $10^{16}$  cm<sup>-3</sup> in unintentionally doped MoS<sub>2</sub>) and  $n_{\rm i}$  is the intrinsic carrier concentration (for MoS<sub>2</sub>,  $n_i \approx 6 \times 10^{15} T^{3/2} \exp\left(-E_{\rm G}/2kT\right) {\rm cm}^{-3}$ ). According to this expression a low value of  $V_{\rm FB,id}$  slightly varying with the T (from -0.35 V at 298 K to -0.42 V at 273 K) would be expected for our device. The negative shift of the experimental  $V_{\rm FB}$  with respect to  $V_{\rm FB,id}$  can be accounted for by the presence of a net positive charge density at the interface with SiO<sub>2</sub> that can be evaluated as  $C_{\rm ox}(V_{\rm FB}-V_{\rm FB,id})/q \approx 2.2 \times 10^{12}$  cm<sup>-2</sup>.

In the following section, the device transfer characteristics above the threshold will be analyzed to extract the threshold voltage and mobility.

### Transfer characteristics above threshold

The linear scale transfer characteristics (Figure 2b) show very low current below a threshold voltage ( $V_{\rm th}$ ) and a nearly linear increase of  $I_{\rm D}$  vs  $V_{\rm G}$  above  $V_{\rm th}$ . Two effects can be observed from the comparison of the  $I_{\rm D}-V_{\rm G}$  curves at increasing temperatures, i.e., (i) a negative shift of the threshold voltage and (ii) a decrease of the  $I_{\rm D}-V_{\rm G}$  curve slope in the linear region above  $V_{\rm th}$ . The origin of these two effects will be discussed more in detail later on. Interestingly, as a result of these two competing effects, the  $I_{\rm D}-V_{\rm G}$  characteristics tend to cross nearly at the same gate bias  $V_{\rm G}=-21$  V (see details in the insert of Figure 2b). This bias condition can be interesting for some ap-

plications where it is desirable that the device performance does not depend significantly on the temperature  $(dI_D/dT \approx 0)$ .

Figure 2c shows the transconductance  $g_{\rm m}$  vs  $V_{\rm G}$  curves calculated by differentiation ( $g_{\rm m}={\rm d}I_{\rm D}/{\rm d}V_{\rm G}$ ) of the  $I_{\rm D}-V_{\rm G}$  characteristics in Figure 2b. In the considered bias range, all the curves exhibit an increase of  $g_{\rm m}$  with  $V_{\rm G}$  up to a maximum value, followed by a decrease of  $g_{\rm m}$ . The maximum transconductance value ( $g_{\rm m,max}$ ) is found to decrease with increasing temperature. Furthermore, a rigid shift of the  $g_{\rm m}-V_{\rm G}$  curves toward negative gate bias values is observed with increasing T.

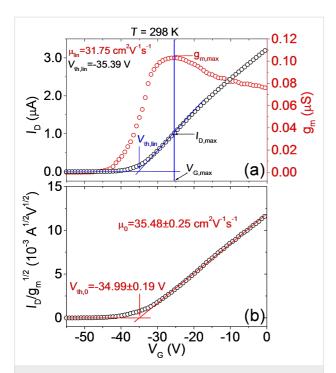

From the linear scale transfer characteristics and the transconductance, two key electrical parameters for transistor operation, i.e., the threshold voltage  $(V_{th})$  and the field effect mobility  $(\mu)$ , are typically evaluated. Figure 4a shows a linear scale plot of  $I_D$ (left axis) and of the transconductance  $g_{\rm m}$  (right axis) at  $V_{\rm DS} = 0.1 \text{ V}$  and T = 298 K. The field effect mobility in the linear region,  $\mu_{lin}$ , of the transfer characteristics is typically extracted from the transconductance using the following formula  $\mu_{lin} = g_m L/(WC_{ox}V_{DS})$ , where L and W are the channel length and width, respectively, and  $C_{ox}$  the SiO<sub>2</sub> gate capacitance. For our device with  $L/W = 7 \mu m/25 \mu m$  and  $C_{ox} \approx$  $9.1 \times 10^{-5}$  F/m<sup>2</sup>, the evaluated mobility from the maximum transconductance value  $g_{m,max}$  was  $\mu_{lin} = 31.75 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , as indicated in Figure 4a. A method for evaluating  $V_{\text{th}}$  consists of drawing the tangent line to the  $I_D$ - $V_G$  curve at the bias ( $V_{G,max}$ ) corresponding to  $g_{m,max}$  and taking the intercept with the  $I_D = 0$ baseline [16], as shown in Figure 4a.

This procedure can be explained by simple geometrical considerations. In the linear region of the transfer characteristics,  $I_D$  can be expressed as [14]:

$$I_{\rm D} = \frac{W}{L} \mu C_{\rm ox} V_{\rm DS} \left( V_{\rm G} - V_{\rm th} \right). \tag{2}$$

Hence, it results that  $I_{D,max} = g_{m,max}(V_{G,max} - V_{th})$  and the threshold voltage can be calculated as

$$V_{\text{th,lin}} = -I_{\text{D.max}}/g_{\text{m.max}} + V_{\text{G.max}} \approx -35.39 \,\text{V}.$$

As a matter of fact, for the evaluation of  $V_{\rm th,lin}$  and  $\mu_{\rm lin}$  based on Equation 2 the contribution of the contact resistance is assumed to be zero. However, as deduced from the analysis of the subthreshold characteristics, a Schottky barrier is associated to the source/drain contacts with MoS<sub>2</sub>, which is also expected to result in a non-negligible contact resistance,  $R_{\rm C}$ . The value of the contact resistance above the threshold and its temperature dependence will be estimated in the last section of this paper from the analysis of the on-resistance ( $R_{\rm on}$ ) extracted from the

**Figure 4:** (a) Linear scale plot of  $I_D$  (left axis) and of the transconductance  $g_m$  (right axis) at  $V_{DS}$  = 0.1 V and T = 298 K. The extraction of the field effect mobility ( $\mu_{lin}$ ) from the maximum of  $g_m$  and of  $V_{th}$  by the linear extrapolation method ( $V_{th,lin}$ ) is illustrated. (b) Plot of  $I_D/g_m^{1/2}$  vs  $V_G$  with illustration of extraction of the mobility ( $\mu_0$ ) and threshold voltage value ( $V_{th,0}$ ) corrected by the effect of the contact resistance ( $R_C$ ).

device output characteristics ( $I_D$ – $V_{DS}$ ) at low  $V_{DS}$ . Here, we want to discuss how  $R_C$  can influence the evaluation of  $\mu$  and  $V_{th}$  from the transfer characteristics.

In order to take into account the role of  $R_C$ ,  $V_{DS}$  can be replaced by  $V_{DS}$ – $I_DR_C$  in Equation 2, and solving by  $I_D$ , the following expression for  $I_D$  is obtained:

$$I_{\rm D} = \frac{\frac{W}{L} \mu_0 C_{\rm ox} V_{\rm DS} \left( V_{\rm G} - V_{\rm th,0} \right)}{1 + \frac{W}{L} \mu_0 C_{\rm ox} R_{\rm c} \left( V_{\rm G} - V_{\rm th,0} \right)},$$

(3)

where  $\mu_0$  and  $V_{\text{th},0}$  represent the values of the mobility and threshold voltage corrected by the effect of  $R_{\text{C}}$ . As a consequence, the transconductance  $g_{\text{m}} = dI_{\text{D}}/dV_{\text{G}}$  can be expressed as:

$$g_{\rm m} = \frac{\frac{W}{L} \mu_0 C_{\rm ox} V_{\rm DS}}{\left[ 1 + \frac{W}{L} \mu_0 C_{\rm ox} R_{\rm c} \left( V_{\rm G} - V_{\rm th,0} \right) \right]^2}.$$

(4)

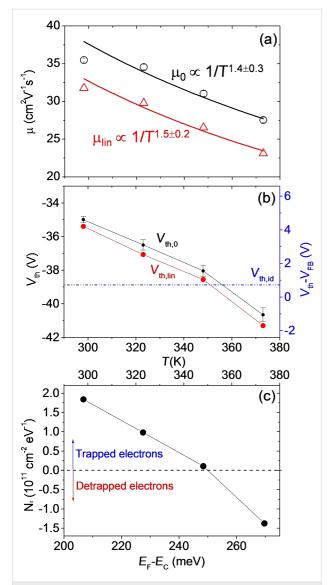

Noteworthy, the ratio  $I_{\rm D}/\sqrt{g_{\rm m}} = \sqrt{W/L \mu_0 C_{\rm ox} V_{\rm DS}} \left(V_{\rm G} - V_{\rm th,0}\right)$ is independent of  $R_{\rm C}$ . A plot of  $I_{\rm D}/g_{\rm m}^{1/2}$  vs  $V_{\rm G}$  is reported in Figure 4b. The corrected value of the field effect mobility  $(\mu_0 = 35.48 \pm 0.25 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1})$  can be calculated from the slope of the linear fit of these data, whereas the threshold voltage  $(V_{\text{th},0} = -34.99 \pm 0.19 \text{ V})$  can be obtained from the intercept with the x axis. It is worth noting that the mobility value  $\mu_0$  after correction for the contact resistance is more than 10% higher than the value estimated without any correction, whereas the threshold voltage V<sub>th.0</sub> after correction is only 1% higher than the value estimated without accounting for  $R_{\rm C}$ . This indicates that the underestimation of the mobility neglecting the contact resistance effect can be quite relevant, whereas the threshold voltage is less affected by  $R_{\rm C}$ . By repeating this procedure for all the measured characteristics reported in Figure 2b,c, the temperature dependence of the mobility ( $\mu_{lin}$  and  $\mu_0$ ), threshold voltage ( $V_{th}$  and  $V_{th,0}$ ) in the considered temperature range has been evaluated, as illustrated in Figure 5a,b, respectively.

Both  $\mu_{lin}$  and  $\mu_0$  were found to decrease as a function of T with a similar dependence  $1/T^{\alpha}$ , with  $\alpha=1.5\pm0.2$  in the case of  $\mu_{lin}$  and  $\alpha=1.4\pm0.3$  in the case of  $\mu_0$ . Such a dependence of  $\mu\approx1/T^{\alpha}$  with  $\alpha>1$  indicates that the main mechanism limiting the mobility of electrons in the multilayer MoS<sub>2</sub> channel in this temperature range is scattering by optical phonons, as reported by other experimental and theoretical investigations [4]. Instead, electron mobility was found to be limited by Coulomb scattering by charged impurities only at lower temperatures (<100 K) [4]. Noteworthy, scattering by charged impurities at the interface with the substrate results in the dominant mechanism for another well-studied 2D material, graphene, even at room temperature and higher temperatures [17,18].

In Figure 5b, the threshold voltage  $V_{\rm th}$  exhibits a negative shift of about 6 V with increasing the temperature from 298 to 273 K. For convenience, the difference  $V_{\rm th}-V_{\rm FB}$  is also reported in Figure 5b, right scale. It is useful to compare the experimental temperature dependence of  $V_{\rm th}$  with the expected theoretical variation with temperature, in order to understand which are the relevant physical parameters ruling this behavior.

For an ideal transistor (without interface states) operating under accumulation conditions, the shift between the threshold voltage  $V_{\rm th,id}$  and the flat band voltage  $V_{\rm FB,id}$  can be expressed as:

$$V_{\text{th,id}} - V_{\text{FB,id}} = \psi_{\text{th}} + \frac{qN_{\text{s}}(\psi_{\text{th}})}{C_{\text{ox}}}$$

(5)

where  $\psi_{th}$  is the downward (negative) band bending at the threshold (as illustrated in the band diagram (iii) of Figure 3c,

Figure 5: (a) Temperature dependence of the field effect mobility extracted from the linear region of the  $I_D$ – $V_G$  characteristics without ( $\mu_{lin}$ ) and with ( $\mu_0$ ) the correction for the effect of the contact resistance  $R_C$ . Experimental data have been fitted with a temperature dependence  $1/T^\alpha$ . (b) Temperature dependence of the threshold voltage evaluated without ( $V_{th,lin}$ ) and with ( $V_{th,0}$ ) the correction for the effect of the contact resistance  $R_C$ . (c) Density of trapped/detrapped electrons at MoS<sub>2</sub>/SiO<sub>2</sub>, as a function of T (upper scale) and the corresponding position of the Fermi level with respect to the conduction band ( $E_F$ – $E_C$ ).

and  $\textit{N}_{s}(\psi_{th})$  is the electron density in the channel at  $\psi_{th}$

$$N_{\rm s}\left(\psi_{\rm th}\right) = \frac{\sqrt{2}\varepsilon_0 \varepsilon_{\rm s}}{kTL_{\rm D}} \sqrt{\left[\exp\left(-\frac{\psi_{\rm th}}{kT}\right) + \frac{\psi_{\rm th}}{kT} - 1\right]}, \quad (6)$$

where  $L_{\rm D} = \sqrt{\epsilon_0 \epsilon_{\rm s} kT/q^2 N_{\rm D}}$  is the Debye length. The band bending  $\psi_{\rm th}$  can be evaluated assuming that the electron density in the channel at the threshold corresponds to  $N_{\rm s}(\psi_{\rm th}) = t N_{\rm D}$ ,

where  $N_{\rm D}$  is the uniform doping concentration in the MoS<sub>2</sub> thin film and t its thickness. Assuming  $N_{\rm D}=10^{16}~{\rm cm}^{-3}$  for our unintentionally doped MoS<sub>2</sub>, we obtain  $N_{\rm s}\approx 4\times 10^{10}~{\rm cm}^{-2}$ . Furthermore, a value of  $\psi_{\rm th}$  ranging from approximately  $-34~{\rm meV}$  (at  $T=298~{\rm K}$ ) to  $-39~{\rm meV}$  (at  $T=373~{\rm K}$ ) can be estimated from the dependence of  $N_{\rm s}$  on  $\psi_{\rm th}$  in Equation 6. Under these assumptions,  $V_{\rm th,id}$ – $V_{\rm FB,id}\approx 0.7~{\rm eV}$  (nearly independent of T) can be estimated, as indicated in Figure 5b (blue dashed line).

In order to account for the large change of  $V_{\rm th}$  with temperature, the role of interface states at SiO<sub>2</sub>/MoS<sub>2</sub> interface must be considered. The difference between the experimental  $V_{\rm th}-V_{\rm FB}$  and theoretical  $V_{\rm th,id}-V_{\rm FB,id}$  can be described by a term  $\Delta V_{\rm it}=qN_{\rm it}/C_{\rm ox}$ , where  $N_{\rm it}$  is the density of trapped/detrapped electrons by SiO<sub>2</sub> interface traps. These interface traps exhibit a donor like behavior, i.e., they are positively charged above the Fermi level (when they are empty) and neutral below the Fermi level (when they are filled by electrons) [13]. Hence, electron trapping results in a neutralization of the interface states, resulting in a positive shift of  $V_{\rm th}$  with respect to  $V_{\rm FB}$  (i.e.  $\Delta V_{\rm it} > 0$ ). On the contrary, detrapping of electrons from these states results in an increase of the positive charge and, hence, in  $\Delta V_{\rm it} < 0$ .

From the experimental data in Figure 5b, trapped electron densities  $N_{\rm it} = 2 \times 10^{11}$ ,  $1 \times 10^{11}$ , and  $2 \times 10^{10}$  cm<sup>-2</sup> are estimated at 298, 323, and 348 K, respectively, whereas a detrapped electron density  $N_{\rm it} = 1.3 \times 10^{11}$  cm<sup>-2</sup> is obtained at 373 K (see Figure 5c). Electron trapping and detrapping at MoS<sub>2</sub>/SiO<sub>2</sub> interface have been shown to be thermally activated processes [13]. Hence, for a given interface trap distribution  $D_{\rm it}$  close to the MoS<sub>2</sub> conduction band,  $N_{\rm it}$  can be expressed as

$$N_{\rm it} = [P_{\rm tr}(T) - P_{\rm det}(T)] \int_{E_{\rm F} - E_{\rm C} + \psi}^{E_{\rm F} - E_{\rm C}} D_{\rm it} d\phi$$

(7)

where  $P_{\rm tr}(T)$  and  $P_{\rm det}(T)$  are the trapping and detrapping probabilities, respectively [13]. The experimentally found temperature dependence of  $N_{\rm it}$  can be explained as follows. As T increases, the shift of the Fermi energy  $E_{\rm F}$  with respect to  $E_{\rm C}$  increases as

$$E_{\mathrm{F}} - E_{\mathrm{C}} = \frac{E_{\mathrm{G}}}{2} - \frac{kT}{q} \ln \left[ \frac{N_{\mathrm{D}}}{n_{\mathrm{i}}(T)} \right]$$

resulting in a change of the integration range in Equation 7. Furthermore, the difference  $P_{\rm tr}(T) - P_{\rm det}(T)$  can change with T. The dependence of  $N_{\rm it}$  on  $E_{\rm F}$  is also illustrated in Figure 5c. It is consistent with a decrease of  $D_{\rm it}$  with increasing  $E_{\rm F} - E_{\rm C}$ .

Furthermore, at 373 K, it can be argued that the  $P_{\rm det}$  becomes higher than  $P_{\rm tr}$ , resulting in a negative value of  $N_{\rm it}$ .

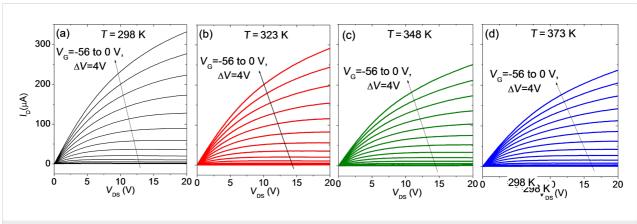

# Output characteristics

Figure 6 shows the output characteristics  $I_{\rm D}-V_{\rm DS}$  for different gate bias values ranging from  $V_{\rm G}=-56$  to 0 V (with steps  $\Delta V=4$  V) measured at different temperatures, i.e., (a) 298 K, (b) 323 K, (c) 348 K and (d) 373 K. For all the  $V_{\rm G}$  values,  $I_{\rm D}$  exhibits a linear increase with  $V_{\rm DS}$  at low drain bias ( $V_{\rm DS} << V_{\rm G}-V_{\rm th}$ ), whereas it deviates from the linear behavior at larger  $V_{\rm DS}$ . In particular, current saturation is achieved whenever the condition  $V_{\rm DS} > V_{\rm G}-V_{\rm th}$  is reached. By comparing the output characteristics measured at the different temperatures with the same  $V_{\rm G}$  values, it is evident that both the slope of the  $I_{\rm D}-V_{\rm DS}$  curves in the linear region and the saturation current value decreases with increasing T.

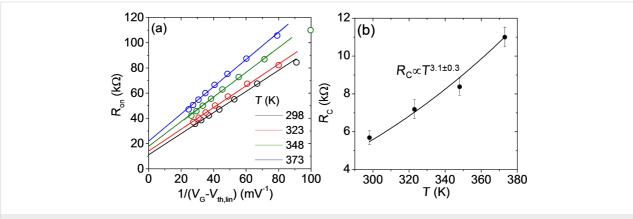

The reciprocal of the  $I_D$ – $V_{DS}$  curves slope in the linear region at low  $V_{DS}$  is the device on-resistance  $R_{on}$ , which can be expressed as:

$$R_{\rm on} = 2R_{\rm C} + \frac{L}{W}R_{\rm ch} = 2R_{\rm C} + \frac{L}{W}\frac{1}{q\mu(V_{\rm G} - V_{\rm th})},$$

(8)

where  $R_{\rm C}$  is the source and drain contact resistance and  $R_{\rm ch}$  the channel sheet resistance, which depends inversely on  $(V_{\rm G}-V_{\rm th})$ , according to Equation 2.

Figure 7a reports the plots of  $R_{\rm on}$  vs  $1/(V_{\rm G}-V_{\rm th,lin})$  extracted from the  $I_{\rm D}-V_{\rm DS}$  characteristics in Figure 6 at the different temperatures. The linear fit of the data was performed for the four temperatures and, from the intercept with the vertical axis, the value of the contact resistance  $R_{\rm C}$  was estimated. The behavior of  $R_{\rm C}$  vs T is reported in Figure 7b, indicating an increase of  $R_{\rm C} \propto T^{\alpha}$ , with  $\alpha = 3.1 \pm 0.3$ .

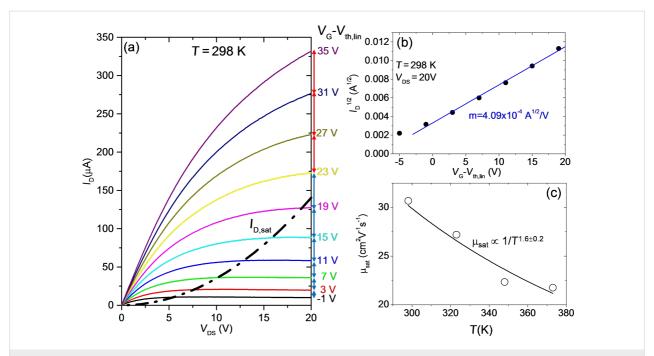

Finally, the behavior of the output characteristics at high  $V_{\rm DS}$  is discussed. Figure 8a shows the  $I_{\rm D}-V_{\rm DS}$  characteristics measured at T=298 K. The  $V_{\rm G}-V_{\rm th}$  value for each curve is indicated. It can be observed that the current saturation regime (i.e.,  $I_{\rm DS}$  in-

Figure 6: Output characteristics  $I_D$ - $V_{DS}$  for different gate bias values from -56 to 0 V at different temperatures: (a) T = 298 K, (b) T = 323 K, (c) T = 348 K and (d) T = 373 K.

Figure 7: (a) On-resistance  $R_{\text{on}}$  vs  $1/(V_{\text{G}}-V_{\text{th,lin}})$  at different temperatures. (b) Temperature dependence of  $R_{\text{C}}$ .

Figure 8: (a) Output characteristics ( $I_D$ - $V_{DS}$ ) for different gate bias values from -56 to 0 V at T = 298 K. (b) Plot of  $I_D^{1/2}$  vs  $V_G$ - $V_{th,lin}$  for  $V_{DS}$  = 20 V and linear fit of the data. (c) Saturation mobility  $\mu_{sat}$  vs temperature.

dependent of  $V_{\rm DS}$ ) is reached only for  $V_{\rm G}$ – $V_{\rm th}$  < 20 V, corresponding to an accumulated electron density in the channel  $N_{\rm s}$  < 1.1 × 10<sup>12</sup> cm<sup>-2</sup>. For  $V_{\rm G}$ – $V_{\rm th}$  > 20 V, saturation is not reached.

In the saturation condition,  $I_{\rm D}$  is only a quadratic function of  $V_{\rm G}$ – $V_{\rm th}$  [14]:

$$I_{\text{D,sat}} = \frac{W}{2BL} \mu_{\text{sat}} C_{\text{ox}} \left( V_{\text{G}} - V_{\text{th}} \right)^2, \tag{9}$$

where  $\mu_{sat}$  is the mobility value under saturation conditions and the term B is the so-called body coefficient, which depends on the gate oxide capacitance, on the doping concentration in the film and on the temperature:

$$B = 1 + \frac{1}{2C_{\text{ox}}} \sqrt{\frac{\varepsilon_0 \varepsilon_s q^2 N_{\text{D}}}{kT \ln \left\lceil N_{\text{D}} / n_{\text{i}} \left(T\right) \right\rceil}}.$$

For thin gate dielectrics and low doping in the film, B can be approximated to 1, but for thick dielectrics and high doping its value can be significantly higher. In the case of our device with  $C_{\rm ox} = 9.1 \times 10^{-5}$  F/m and assuming a MoS<sub>2</sub> doping  $N_{\rm D} \approx 1 \times 10^{16}$  cm<sup>-3</sup>, B can range from  $\approx 2.97$  to  $\approx 3.12$  in the considered temperature range. In Figure 8b,  $I_{\rm D}^{1/2}$  at  $V_{\rm DS} = 20$  V is reported as a function of  $V_{\rm G}$ – $V_{\rm th}$ , showing a linear behavior. According to Equation 9, the mobility under saturation condi-

tion can be evaluated from the slope m of the fit, as  $\mu_{\rm sat} = 2BLm^2/WC_{\rm ox}$ . By repeating this procedure for all the output characteristics measured at the different temperatures, the behavior of  $\mu_{\rm sat}$  as a function of T can be obtained. The main error source in the estimation of  $\mu_{\rm sat}$  is related to the fact that the doping concentration  $N_{\rm D}$  and, hence, the coefficient B is not exactly known. Noteworthy, the values of  $\mu_{\rm sat}$  in Figure 8c, estimated assuming  $N_{\rm D}\approx 1\times 10^{16}~{\rm cm}^{-3}$ , are very close to those evaluated from the linear region of the transfer characteristics (see Figure 5a) and exhibit a similar temperature dependence. This also confirms that the assumption for the doping concentration is correct.

#### Conclusion

In conclusion, a temperature dependent investigation of backgated multilayer MoS<sub>2</sub> transistors with Ni source/drain contacts in the range from T=298 to 373 K has been performed. The SBH  $\Phi_{\rm B}\approx 0.18$  eV of the Ni/MoS<sub>2</sub> contact was evaluated from the analysis of the transfer characteristics  $I_{\rm D}-V_{\rm G}$  in the subthreshold regime. The resulting  $R_{\rm C}$  associated with the SBH was determined by fitting the  $R_{\rm on}$  dependence on  $1/(V_{\rm G}-V_{\rm th})$  extracted from the device output characteristics  $I_{\rm D}-V_{\rm DS}$  at low  $V_{\rm DS}$ . An increase of  $R_{\rm C} \propto T^{3.1}$  was demonstrated. The impact of  $R_{\rm C}$  on the values of  $\mu$  and  $V_{\rm th}$  values was determined, showing an underestimation of  $\mu$  by more than 10% if the effect of  $R_{\rm C}$  is neglected, whereas the influence of  $R_{\rm C}$  on the estimated value of  $V_{\rm th}$  is only 1%. Furthermore, the temperature dependence of  $\mu$  and  $V_{\rm th}$  was investigated, showing a decrease of

$\mu \approx 1/T^{\alpha}$  with  $\alpha = 1.4 \pm 0.3$  (indicating scattering by optical phonons as the limiting mechanism), and a negative shift of  $V_{\rm th}$  by about 6 V with increasing T. The role played by electron trapping at the MoS<sub>2</sub>/SiO<sub>2</sub> interface to explain such a large  $V_{\rm th}$  shift was discussed.

## Experimental

Back-gated transistors were fabricated using MoS $_2$  flakes exfoliated from molybdenite bulk crystals (supplier SPI [19]) with thicknesses ranging from  $\approx$ 40 to  $\approx$ 50 nm and transferred onto a highly doped n-type Si substrate covered with 380 nm of thermally grown SiO $_2$ . An accurate sample preparation protocol has been adopted for controlled quality of the MoS $_2$ /SiO $_2$  interface, as this is crucial to achieve reproducible electrical behavior of the devices. In particular, thermo-compression printing using a Karl-Suss nanoimprint device with fixed temperature and pressure conditions [20,21] has been employed to transfer the exfoliated MoS $_2$  flakes onto the SiO $_2$  surface that was previously cleaned using solvents and a soft O $_2$  plasma treatment. Finally, source and drain contacts were obtained by deposition and lift-off of a Ni(50 nm)/Au(100 nm) bilayer.

The temperature-dependent electrical characterization in the range from 298 to 373 K was performed using a Cascade Microtech probe station with an Agilent 4156b parameter analyzer. All the measurements were carried out in dark conditions and under nitrogen flux.

# Acknowledgements

P. Fiorenza, I. Deretzis, A. La Magna, C. Bongiorno and G. Nicotra from CNR-IMM are acknowledged for helpful discussions. This work has been supported, in part, by MIUR in the framework of the FlagERA project "GraNitE: Graphene heterostructures with Nitrides for high frequency Electronics" (Grant number 0001411).

# References

- Geim, A. K.; Grigorieva, I. V. Nature 2013, 499, 419–425. doi:10.1038/nature12385

- Wang, Q. H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J. N.; Strano, M. S. Nat. Nanotechnol. 2012, 7, 699–712. doi:10.1038/nnano.2012.193

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Nat. Nanotechnol. 2011, 6, 147–150. doi:10.1038/nnano.2010.279

- Kim, S.; Konar, A.; Hwang, W.-S.; Lee, J. H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J.-B.; Choi, J.-Y.; Jin, Y. W.; Lee, S. Y.; Jena, D.; Choi, W.; Kim, K. *Nat. Commun.* 2012, 3, No. 1011. doi:10.1038/ncomms2018

- Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. Nano Lett. 2013, 13, 100–105. doi:10.1021/nl303583v

- Giannazzo, F.; Fisichella, G.; Piazza, A.; Agnello, S.; Roccaforte, F. Phys. Rev. B 2015, 92, 081307. doi:10.1103/PhysRevB.92.081307

- 7. McDonnell, S.; Addou, R.; Buie, C.; Wallace, R. M.; Hinkle, C. L. ACS Nano **2014**, *8*, 2880–2888. doi:10.1021/nn500044q

- Jiang, C.; Rumyantsev, S. L.; Samnakay, R.; Shur, M. S.; Balandin, A. A. J. Appl. Phys. 2015, 117, 064301. doi:10.1063/1.4906496

- Kwon, H.-J.; Jang, J.; Kim, S.; Subramanian, V.; Grigoropoulos, C. P. Appl. Phys. Lett. 2014, 105, 152105. doi:10.1063/1.4898584

- Giannazzo, F.; Fisichella, G.; Piazza, A.; Di Franco, S.; Greco, G.;

Agnello, S.; Roccaforte, F. *Phys. Status Solidi RRL* 2016, 10, 797–801.

doi:10.1002/pssr.201600209

- Late, D. J.; Liu, B.; Ramakrishna Matte, H. S. S.; Dravid, V. P.;

Rao, C. N. R. ACS Nano 2012, 6, 5635–5641. doi:10.1021/nn301572c

- Choi, K.; Raza, S. R. A.; Lee, H. S.; Jeon, P. J.; Pezeshki, A.;

Min, S.-W.; Kim, J. S.; Yoon, W.; Ju, S.-Y.; Lee, K.; Im, S. Nanoscale

2015. 7 5617–5623 doi:10.1039/C4NR06707.1

- Guo, Y.; Wei, X.; Shu, J.; Liu, B.; Yin, J.; Guan, C.; Han, Y.; Gao, S.;

Chen, Q. Appl. Phys. Lett. 2015, 106, 103109. doi:10.1063/1.4914968

- Park, Y.; Baac, H. W.; Heo, J.; Yoo, G. Appl. Phys. Lett. 2016, 108, 083102. doi:10.1063/1.4942406

- Sze, S. M.; Ng, K. K. Physics of Semiconductor Devices, 3rd ed.;

Wilev: New York. 2007.

- Schroder, D. K. Semiconductor Material and Device Characterization, 3rd ed.; Wiley: Hoboken, NJ, 2006.

- Giannazzo, F.; Sonde, S.; Lo Nigro, R.; Rimini, E.; Raineri, V.

Nano Lett. 2011, 11, 4612–4618. doi:10.1021/nl2020922

- Sonde, S.; Giannazzo, F.; Vecchio, C.; Yakimova, R.; Rimini, E.;

Raineri, V. Appl. Phys. Lett. 2010, 97, 132101. doi:10.1063/1.3489942

- 19. SPI Supplies. http://www.2spi.com (accessed Dec 30, 2016).

- 20. Giannazzo, F.; Fisichella, G.; Piazza, A.; Di Franco, S.; Oliveri, I. P.; Agnello, S.; Roccaforte, F. Mater. Sci. Semicond. Process. 2016, 42, 174–178. doi:10.1016/j.mssp.2015.07.062

- Fisichella, G.; Di Franco, S.; Roccaforte, F.; Ravesi, S.; Giannazzo, F.

Appl. Phys. Lett. 2014, 104, 233105. doi:10.1063/1.4882165

## License and Terms

This is an Open Access article under the terms of the Creative Commons Attribution License (<a href="http://creativecommons.org/licenses/by/4.0">http://creativecommons.org/licenses/by/4.0</a>), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The license is subject to the *Beilstein Journal of Nanotechnology* terms and conditions: (http://www.beilstein-journals.org/bjnano)

The definitive version of this article is the electronic one which can be found at: doi:10.3762/bjnano.8.28